## Exam 3

## 601.428/628 Compilers and Interpreters

December 21, 2021

Complete all questions.

Closed book, no use of electronic resources is permitted.

You may use two sheets of hand-written notes.

Time: 90 minutes.

I affirm that I have completed this exam without unauthorized assistance from any person, materials, or device.

Signed: \_\_\_\_\_

Print name: \_\_\_\_\_

Date: \_\_\_\_\_

## Reference

| Instruction |             | Meaning                                                                       |

|-------------|-------------|-------------------------------------------------------------------------------|

| ldci        | Vrd, \$N    | Store integer constant \$N to <i>Vrd</i>                                      |

| addi        | Vrd, Op, Op | Store sum of operands to Vrd                                                  |

| subi        | Vrd, Op, Op | Store difference of operands (left - right) to Vrd                            |

| muli        | Vrd, Op, Op | Store product of operands to <i>Vrd</i>                                       |

| divi        | Vrd, Op, Op | Store result of dividing operands (left / right) to Vrd                       |

| modi        | Vrd, Op, Op | Store remainder after dividing operands (left / right) to Vrd                 |

| negi        | Vrd, Op     | Store negation of operand to Vrd                                              |

| localaddr   | Vrd, \$N    | Store address of memory location at offset of \$N bytes                       |

|             |             | into local memory storage area to Vrd                                         |

| ldi         | Vrd, (Vra)  | Store value loaded from memory location (Vra) to Vrd                          |

| sti         | (Vra), Vrb  | Store value in <i>Vrb</i> to memory location ( <i>Vra</i> )                   |

| readi       | Vrd         | Read integer input value and store it to Vrd                                  |

| writei      | Vra         | Write integer value in <i>Vra</i> to output                                   |

| jmp         | label       | Unconditional jump to <i>label</i>                                            |

| cmpi        | Ор, Ор      | Compare operands                                                              |

| je          | label       | Conditional jump to <i>label</i> if in previous comparison, left = right      |

| jne         | label       | Conditional jump to <i>label</i> if in previous comparison, left $\neq$ right |

| jlt         | label       | Conditional jump to <i>label</i> if in previous comparison, left < right      |

| jlte        | label       | Conditional jump to <i>label</i> if in previous comparison, left $\leq$ right |

| jgt         | label       | Conditional jump to <i>label</i> if in previous comparison, left > right      |

| jgte        | label       | Conditional jump to <i>label</i> if in previous comparison, left $\geq$ right |

| mov         | Vrd, Vra    | Store value in Vra to Vrd                                                     |

Reference for high-level instructions:

Notes:

- Virtual registers are vr0, vr1, etc.

- *Vrd* means a destination virtual register (modified by the instruction)

- *Vra* and *Vrb* are source virtual registers (not modified by the instruction)

- (*Vra*) and (*Vrb*) mean a memory reference using a virtual register as a pointer, e.g., (vr0)

- \$N means an integer constant (e.g, \$42)

- *Op* means a source operand (either source virtual register or integer constant)

- *label* means a target label

- All values are 64-bit signed integers

**Question 1**. [25 points] Consider the following high-level basic block:

|     |           | 0,2                          |

|-----|-----------|------------------------------|

| 1:  | localaddr | •                            |

| 2:  | ldci      | 0,2, 13<br>vr14, \$10        |

| 3:  | muli      | 0,2,13,14<br>vr15, vr0, vr14 |

| 4:  | addi      | 0,2,13,15<br>vr16, vr15, vr2 |

| 5:  | muli      | 0,2,13,16<br>vr17, vr16, \$8 |

| 6:  | addi      | 0,2,3,17<br>vr18, vr13, vr17 |

| 7:  | ldi       | 0,2,18<br>vr3, (vr18)        |

| 8:  | ldci      | 0,2,3<br>vr19, \$0           |

| 9:  | mov       | 0,2,3, 19<br>vr1, vr19       |

| 10: | jmp       | 0,1,2,3<br>.L16<br>0,1,2,3   |

|     |           |                              |

Assume that vr0, vr1, vr2, and vr3 are live at the end of the basic block.

Show:

- 1. The virtual registers that are live at the beginning of the block

- 2. For each instruction in the block, which virtual registers are live at the point *just after* the instruction

Recall that a virtual register is live it will be used at a later point, but there is not an intervening def (assignment) of the virtual register.

Question 2. [25 points] Assume that the following code is a basic block:

| ldci   | vr4, | \$3  |     |

|--------|------|------|-----|

| ldci   | vr5, | \$2  |     |

| muli   | vr6, | vr4, | vr5 |

| addi   | vr7, | vr0, | vr6 |

| writei | vr7  |      |     |

Assume that vr4, vr5, vr6, or vr7 are temporaries, so they are all dead at the end of the block.

(a) Rewrite this code so that all uses of virtual registers with known constant values are replaced with the appropriate constant. For example, in an instruction mov vr8, vr9, if vr9 is known to have the constant value 42, then you would rewrite the instruction as mov vr8, \$42. Note that if a value is computed from constant operands, the computed value should also be treated as a constant (constant folding.)

(b) Which instructions in the transformed code can be eliminated? Explain briefly.

Instructions marked with an X above can be eliminated because they are stores to dead virtual registers.

**Question 3**. [20 points] Assume that a local register allocator has three machine registers available, called A, B, and C. For each the following instructions, we want the local register allocator to assign a machine register for each virtual register. The first instruction is annotated to show that vr0 has been assigned machine register A.

| ast 1 | Instruction        | Register assignments     | Spill and/or restore?                 |

|-------|--------------------|--------------------------|---------------------------------------|

| المع  | ldci vr0, \$1      | vr0→A                    |                                       |

| ]     | ldci vr1, \$2      | Vr0-1A, vr1-9B           |                                       |

| ]     | ldci vr2, \$2      | Vr0->A, url->B, vr2->    | pill vr2,C                            |

| ĉ     |                    | vr O-A, ur (-) B, vr 3-9 | · · · · · · · · · · · · · · · · · · · |

| n     | nuli vr4, vr3, \$8 | vr4 >> A, vr3 >> C       | estore vr2, B                         |

|       |                    | vr4-74, vr)->8, vr       |                                       |

Complete the table above by performing local register allocation. For each instruction in the block, show a possible assignment of machine registers to the referenced virtual registers. Use bottom-up allocation, so that when a spill is necessary, the live virtual register whose next use is furthest in the future is selected as a victim.

Indicate where spills and restores are necessary. You can use the notation spill VR,MR and restore VR,MR, where VR is the virtual register being spilled or restored, and MR is the machine register assignment being removed by the spill or established by the restore.

Don't forget to reclaim machine registers after the last use of the virtual register to which the machine register is assigned.

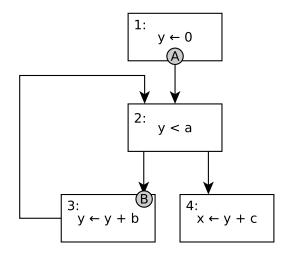

**Question 4**. [20 points] Consider the control-flow graph on the right, where block  $\boxed{1}$  is the entry block and block  $\boxed{4}$  is the exit block, and the variables are a, b, c, x, and y:

(a) At the point labeled (A) (end of block 1), which variables are guaranteed to be used on some forward path? (I.e., which variables are guaranteed to be used at some point in the future?)

(b) At the point labeled (B) (beginning of block (3)), which variables are guaranteed to be used on some forward path?

$$\{a, b, c, y\}$$

(c) Would a dataflow analysis to find guaranteed uses of variables be a forward analysis or a backward analysis? Explain briefly.

Backwards: we want to know what uses will occur in the future, so we need to work backwards

(d) Would a dataflow analysis to find guaranteed uses of variables be a "may" analysis or a "must" analysis? Explain briefly.

**Question 5**. [10 points] Local value numbering (LVN) is useful for detecting redundant computations and replacing them with a use of a previously-computed value.

One potential obstacle to using LVN to eliminate redundant computations is that a storage location (i.e., virtual register) containing a computed value might be overwritten. For example, consider the following code:

| 1: | addi   | vr4, vr5, \$42 |

|----|--------|----------------|

| 2: | writei | vr4            |

| 3: | ldci   | vr4, \$17      |

| 4: | addi   | vr6, vr5, \$42 |

| 5: | writei | vr6            |

At line 4, there is a recomputation of the sum vr5 + 42, which is a value that was previously stored in vr4. However, because vr4 was modified at line 3, it is not correct to replace the instruction at line 4 with

mov vr6, vr4

or to replace the instruction at line 5 with

writei vr4

State whether you think this is a significant problem in practice. I.e., is it likely that computed values will become unavailable by being overwritten, or could the compiler guarantee that this will not happen? Hint: think about how code generation for expression evaluation and address computation works. Briefly justify your answer.

No, it shouldn't be a problem. If, when geventing code to evaluate an expression or compute an address, the code generator consistently allocates a new Virtual negister for each computed value, and never re-uses a virtual register, computed values will never be destroyed. [Extra page for answers and/or scratch work.]